# NRC Publications Archive Archives des publications du CNRC

# Hardware selection recommendations for the NRC Segment Wave Generator Control System Laurich, P.

For the publisher's version, please access the DOI link below./ Pour consulter la version de l'éditeur, utilisez le lien DOI ci-dessous.

# Publisher's version / Version de l'éditeur:

https://doi.org/10.4224/8894882

Contractor Report (National Research Council of Canada. Institute for Ocean Technology); no. CR-2005-01, 2005

NRC Publications Archive Record / Notice des Archives des publications du CNRC : https://nrc-publications.canada.ca/eng/view/object/?id=d67684ec-72a7-48b5-a600-99a1a569f2bd https://publications-cnrc.canada.ca/fra/voir/objet/?id=d67684ec-72a7-48b5-a600-99a1a569f2bd

Access and use of this website and the material on it are subject to the Terms and Conditions set forth at <a href="https://nrc-publications.canada.ca/eng/copyright">https://nrc-publications.canada.ca/eng/copyright</a> READ THESE TERMS AND CONDITIONS CAREFULLY BEFORE USING THIS WEBSITE.

L'accès à ce site Web et l'utilisation de son contenu sont assujettis aux conditions présentées dans le site <u>https://publications-cnrc.canada.ca/fra/droits</u> LISEZ CES CONDITIONS ATTENTIVEMENT AVANT D'UTILISER CE SITE WEB.

Questions? Contact the NRC Publications Archive team at

PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca. If you wish to email the authors directly, please see the first page of the publication for their contact information.

**Vous avez des questions?** Nous pouvons vous aider. Pour communiquer directement avec un auteur, consultez la première page de la revue dans laquelle son article a été publié afin de trouver ses coordonnées. Si vous n'arrivez pas à les repérer, communiquez avec nous à PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca.

National Research Council Canada

Institute for Ocean Technology Conseil national de recherches Canada Institut des technologies océaniques

# **DOCUMENTATION PAGE**

| REPORT NUMBE                                                                                                                                                                                                 | R                                                                                                                                                                                                                                              | NRC REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                              | DATE                                                                                                                                                                   |                                                                                                                                                                                            |                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| CR-2005-01                                                                                                                                                                                                   |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                | March 20                                                                                                                                                               | 005                                                                                                                                                                                        |                                                           |  |

|                                                                                                                                                                                                              | ITY CLASSIFICAT                                                                                                                                                                                                                                | DISTRIBU                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| Unclassified                                                                                                                                                                                                 |                                                                                                                                                                                                                                                | Unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                      | d                                                                                                                                                                      |                                                                                                                                                                                            |                                                           |  |

| TITLE<br>HARDWARE SELECTION RECOMMENDATIONS FOR THE                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| NRC SEGME                                                                                                                                                                                                    |                                                                                                                                                                                                                                                | NERATOR CONTROL SYSTE                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| Final Report<br>AUTHOR(S)                                                                                                                                                                                    |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| Author(3)                                                                                                                                                                                                    |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| Peter Laurich                                                                                                                                                                                                |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| CORPORATE AU                                                                                                                                                                                                 | ITHOR(S)/PERFOR                                                                                                                                                                                                                                | MING AGENCY(S)                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| BA Technolog                                                                                                                                                                                                 | gies                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| PUBLICATION                                                                                                                                                                                                  |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

|                                                                                                                                                                                                              |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| SPONSORING A                                                                                                                                                                                                 | GENCY(S)                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

|                                                                                                                                                                                                              |                                                                                                                                                                                                                                                | gy, National Research Council                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| IOT PROJECT NU                                                                                                                                                                                               | UMBER                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                | NRC FILE NU                                                                                                                                                            | MBER                                                                                                                                                                                       |                                                           |  |

| 42_2076_10                                                                                                                                                                                                   |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| KEY WORDS                                                                                                                                                                                                    |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                | PAGES                                                                                                                                                                  | FIGS.                                                                                                                                                                                      | TABLES                                                    |  |

|                                                                                                                                                                                                              | 1 15                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |                                                                                                                                                                                            |                                                           |  |

| wave generate                                                                                                                                                                                                | or control syste                                                                                                                                                                                                                               | m                                                                                                                                                                                                                                                                                                                                                                                                                                              | i, 15,<br>App. A                                                                                                                                                       |                                                                                                                                                                                            | 15                                                        |  |

| wave generat                                                                                                                                                                                                 | or control syste                                                                                                                                                                                                                               | m                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                        |                                                                                                                                                                                            | 15                                                        |  |

| SUMMARY                                                                                                                                                                                                      |                                                                                                                                                                                                                                                | ed the second generation of its                                                                                                                                                                                                                                                                                                                                                                                                                | App. A                                                                                                                                                                 | ol system fo                                                                                                                                                                               |                                                           |  |

| SUMMARY<br>In early 1991,<br>segmented wa                                                                                                                                                                    | NRC develope<br>ave generators                                                                                                                                                                                                                 | ed the second generation of its<br>. The design used off-the-shell                                                                                                                                                                                                                                                                                                                                                                             | App. A<br>digital contro<br>f technology                                                                                                                               | <ul> <li>both hard</li> </ul>                                                                                                                                                              | or                                                        |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software                                                                                                                                                    | NRC develope<br>ave generators<br>– to the extent                                                                                                                                                                                              | ed the second generation of its<br>. The design used off-the-shell<br>possible at the time. The syste                                                                                                                                                                                                                                                                                                                                          | App. A<br>digital contro<br>f technology<br>m was base                                                                                                                 | – both hard<br>d on the                                                                                                                                                                    | or                                                        |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software                                                                                                                                                    | NRC develope<br>ave generators<br>– to the extent                                                                                                                                                                                              | ed the second generation of its<br>. The design used off-the-shell                                                                                                                                                                                                                                                                                                                                                                             | App. A<br>digital contro<br>f technology<br>m was base                                                                                                                 | – both hard<br>d on the                                                                                                                                                                    | or                                                        |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha                                                                                                                 | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w                                                                                                                                                           | ed the second generation of its<br>. The design used off-the-shell<br>possible at the time. The syste<br>bus) and the pSOS real-time o<br>vell but all of the hardware has                                                                                                                                                                                                                                                                     | App. A<br>digital contro<br>f technology<br>m was base<br>perating sys<br>now been d                                                                                   | – both hard<br>d on the<br>tem.<br>iscontinued                                                                                                                                             | or<br>dware<br>d. The                                     |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha<br>operating syst                                                                                               | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is                                                                                                                                        | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time o<br>vell but all of the hardware has<br>in maintenance-only mode an                                                                                                                                                                                                                                      | App. A<br>digital contro<br>f technology<br>m was base<br>operating sys<br>now been di<br>d the softwa                                                                 | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re developing</li> </ul>                                                                                  | or<br>dware<br>d. The<br>ment                             |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha<br>operating syst<br>environment is                                                                             | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun                                                                                                                     | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has bec                                                                                                                                                                                                 | App. A<br>digital contro<br>technology<br>m was base<br>operating sys<br>now been d<br>d the softwa<br>come impera                                                     | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re developi</li> <li>tive that the</li> </ul>                                                             | or<br>dware<br>d. The<br>ment<br>e                        |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha<br>operating syst<br>environment is<br>control system                                                           | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded                                                                                                    | ed the second generation of its<br>. The design used off-the-shell<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has bee<br>to use current technology – bo                                                                                                                                                               | App. A<br>digital contro<br>f technology<br>m was base<br>perating sys<br>now been d<br>d the softwa<br>come impera<br>th hardware                                     | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re developed</li> <li>tive that the</li> <li>and softward</li> </ul>                                      | or<br>dware<br>d. The<br>ment<br>e<br>are.                |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software -<br>original VME s<br>The system ha<br>operating syste<br>environment is<br>control system<br>This report de                                      | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded<br>eals with the sel                                                                               | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has be<br>to use current technology – bo                                                                                                                                                                | App. A<br>digital contro<br>f technology<br>m was base<br>perating sys<br>now been di<br>d the softwa<br>come impera<br>th hardware                                    | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re develope</li> <li>tive that the</li> <li>and software</li> <li>em. Hardw</li> </ul>                    | or<br>dware<br>d. The<br>ment<br>e<br>are.<br>vare        |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha<br>operating syste<br>environment is<br>control system<br>This report de<br>must be selec                       | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded<br>eals with the sel                                                                               | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has be<br>to use current technology – bo<br>lection of new hardware for the<br>areness of the options for the p                                                                                         | App. A<br>digital contro<br>f technology<br>m was base<br>operating sys<br>now been di<br>d the softwa<br>come impera<br>th hardware<br>e control syst<br>new operatin | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re develope</li> <li>tive that the</li> <li>and software</li> <li>em. Hardw</li> <li>g system.</li> </ul> | or<br>dware<br>d. The<br>ment<br>e<br>are.<br>vare<br>The |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha<br>operating syste<br>environment is<br>control system<br>This report de<br>must be selec                       | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded<br>eals with the sel<br>sted with an awa                                                           | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has been<br>to use current technology – bo<br>lection of new hardware for the<br>areness of the options for the r<br>stem will, however, be complet                                                     | App. A<br>digital contro<br>f technology<br>m was base<br>operating sys<br>now been di<br>d the softwa<br>come impera<br>th hardware<br>e control syst<br>new operatin | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re develope</li> <li>tive that the</li> <li>and software</li> <li>em. Hardw</li> <li>g system.</li> </ul> | or<br>dware<br>d. The<br>ment<br>e<br>are.<br>vare<br>The |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software<br>original VME s<br>The system ha<br>operating syste<br>environment is<br>control system<br>This report de<br>must be selec                       | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded<br>eals with the sel<br>ted with an aw<br>be operating system<br>National Rese                     | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has be<br>to use current technology – bo<br>lection of new hardware for the<br>areness of the options for the p<br>stem will, however, be complet                                                       | App. A<br>digital contro<br>f technology<br>m was base<br>operating sys<br>now been di<br>d the softwa<br>come impera<br>th hardware<br>e control syst<br>new operatin | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re develope</li> <li>tive that the</li> <li>and software</li> <li>em. Hardw</li> <li>g system.</li> </ul> | or<br>dware<br>d. The<br>ment<br>e<br>are.<br>vare<br>The |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software -<br>original VME s<br>The system ha<br>operating syste<br>environment is<br>control system<br>This report de<br>must be select<br>selection of th | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded<br>eals with the sel<br>ted with an awa<br>be operating system<br>National Rese<br>Institute for O | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has be<br>to use current technology – bo<br>lection of new hardware for the<br>areness of the options for the<br>stem will, however, be complet<br>earch Council<br>cean Technology                     | App. A<br>digital contro<br>f technology<br>m was base<br>operating sys<br>now been di<br>d the softwa<br>come impera<br>th hardware<br>e control syst<br>new operatin | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re develope</li> <li>tive that the</li> <li>and software</li> <li>em. Hardw</li> <li>g system.</li> </ul> | or<br>dware<br>d. The<br>ment<br>e<br>are.<br>vare<br>The |  |

| SUMMARY<br>In early 1991,<br>segmented wa<br>and software -<br>original VME s<br>The system ha<br>operating syste<br>environment is<br>control system<br>This report de<br>must be select<br>selection of th | NRC develope<br>ave generators<br>– to the extent<br>standard (VME<br>as performed w<br>tem software is<br>s no longer fun<br>n be upgraded<br>eals with the sel<br>ted with an awa<br>be operating system<br>National Rese<br>Institute for O | ed the second generation of its<br>. The design used off-the-shelf<br>possible at the time. The syste<br>bus) and the pSOS real-time of<br>vell but all of the hardware has<br>in maintenance-only mode an<br>ctional or supported. It has be<br>to use current technology – bo<br>ection of new hardware for the<br>areness of the options for the<br>stem will, however, be complet<br>earch Council<br>cean Technology<br>, P. O. Box 12093 | App. A<br>digital contro<br>f technology<br>m was base<br>operating sys<br>now been di<br>d the softwa<br>come impera<br>th hardware<br>e control syst<br>new operatin | <ul> <li>both hard</li> <li>d on the</li> <li>tem.</li> <li>iscontinued</li> <li>re develope</li> <li>tive that the</li> <li>and software</li> <li>em. Hardw</li> <li>g system.</li> </ul> | or<br>dware<br>d. The<br>ment<br>e<br>are.<br>vare<br>The |  |

National Research Council Conseil national de recherches Canada

Institute for Ocean Technology

Canada Institut des technologies océaniques

# HARDWARE SELECTION RECOMMENDATIONS FOR THE NRC SEGMENT WAVE GENERATOR CONTROL SYSTEM

**Final Report**

CR-2005-01

Peter Laurich BA Technologies

March 2005

÷

# Hardware Selection Recommendations For the NRC Segment Wave Generator Control System

Version: 1.00 Status: Final

March 29, 2004

Prepared by BA Technologies

# **Table of Contents**

| Table of Conter | nts                         | i |

|-----------------|-----------------------------|---|

| 1. Introduction | )n                          | 1 |

| 2. Current Sy   | vstem Configuration         | 2 |

| 2.1. Hardy      | ware                        | 2 |

| 2.2. Opera      | ating System Software       | 3 |

| 3. Backplane    | Standard Analysis           | 4 |

| 4. VME bus      | Options                     | 5 |

| 4.1. CPU        | Boards                      | 5 |

| 4.1.1. I        | Ranking Process             | 5 |

| 4.1.2.          | Гор Three                   | 7 |

| 4.2. Digita     | al I/O                      | 8 |

| 4.3. Analo      | og I/O                      | 8 |

| 4.3.1. <b>(</b> | Carrier Packs               | 8 |

| 4.3.2. A        | Analog Input                | 8 |

| 4.3.3. A        | Analog Output               | 8 |

| 4.4. VME        | Recommendation              | 9 |

| 5. cPCI Optio   | ons1                        | 0 |

| 5.1. CPU        | Boards1                     | 0 |

| 5.1.1. H        | Ranking Process1            | 0 |

| 5.2. Digita     | al I/O1                     | 1 |

| 5.3. Analo      | og I/O1                     | 1 |

| 5.3.1.          | Carrier Packs1              | 1 |

| 5.3.2. A        | Analog Input1               | 1 |

| 5.3.3. A        | Analog Output1              | 1 |

| 5.4. 6U cF      | PCI Recommendation1         | 1 |

| 5.4.1. 3        | 3U cPCI Option1             | 2 |

| 5.5. Custo      | m Digital Board1            | 3 |

| 6. Final Reco   | mmendations1                | 4 |

| 6.1. Points     | s to Note1                  | 5 |

| 7. Appendix     | A CPU Features and Ranking1 | 6 |

# 1. Introduction

In early 1991, NRC developed the second generation of its digital control system for segmented wave generators. The design used off-the-shelf technology – both hardware and software – to the extent possible at the time. The system was based on the original VME standard (VMEbus) and the pSOS real-time operating system.

The system has performed well but all of the hardware has now been discontinued. The operating system software is in maintenance-only mode and the software development environment is no longer functional or supported. It has become imperative that the control system be upgraded to use current technology – both hardware and software.

This report deals with the selection of new hardware for the control system. Hardware must be selected with an awareness of the options for the new operating system. The selection of the operating system will, however, be completed in a follow-on phase.

The strategy used in developing the hardware recommendations were:

- Extract the specifications from the existing control system

- Examine recent trends in backplane technology, hardware technology and operating system technology

- Develop a short list of candidate hardware choices

- Develop system costs

- Propose a final recommendation based on the information collected

# 2. Current System Configuration

# 2.1. Hardware

The current NRC segmented wave generator control system includes the following board-level products per MCU:

- Force processor board: CPU-40 B/16

- Acromag digital I/O board: AVME 9481

- One Acromag analog input board for every type of feedback device used by the control system: AVME 9330

- One Acromag analog output board for every 8 segments controlled by the MCU (the system supports a maximum of 32 segments per MCU): AVME 9210

- Custom digital board (either NRC IMD or Davis Engineering)

CPU Board (specs reflect the current board):

- 68040 CPU running at 25 MHz with a 4 Kbyte instruction cache and a 4 Kbyte data cache the floating point component is required

- DMA controller

- 4 serial I/O channels, 2 of which are in use. One is used for terminal I/O and the second is used for synch signals (drive signal start and 100 Hz clock)

- 10 Mbps Ethernet port with 64 Kbyte data buffer

- Memory:

- 128 Kbyte SRAM with battery backup

- 128 Kbyte FLASH

- 16 Mbyte DRAM

- 1 boot EPROM for local booting

- 2 boot EPROMs for application booting

# Digital I/O Board:

- 6 digital output signals

- Sink up to 100 mA

Analog Input Boards:

- 32 single-ended channels

- High-level voltage input (+/- 10V range)

- 16-bit resolution

- Sampling rate of up to 30kHz

- External connections via a rear connector (P2)

Analog Output Boards

- 8 output channels per board

- High-level voltage output (+/- 5V range)

- 12-bit resolution

- Settling time less than 6 microseconds

- External connections via a rear connector (P2)

System Chassis:

- Sufficient slots for a controller including:

- 1 processor board

- Up to 3, 32-channel analog input boards

- Up to 4, 8-channel analog output boards

- 1 digital I/O board for up to 6 signals (handles up to 64 signals of I/O)

- 1 custom digital board (board takes only power from the backplane)

# 2.2. Operating System Software

The control system software uses the pSOS operating system. The rights to the operating system have been purchased by Wind River, the developer of VxWorks. Wind River has maintained support for pSOS but there is no new investment in the software – pSOS is no longer a suitable candidate for real-time operating systems for new designs.

The operating system components used in the segmented wave generator control software are shown in the table below. The functionality provided by each of these components would be required in any replacement RTOS being considered

| Component | Description          | Calls      | Description                                |

|-----------|----------------------|------------|--------------------------------------------|

| pSOS      | Operating system     | ev_receive | Wait for an event                          |

|           | kernel               | ev_send    | Send an event                              |

|           |                      | k_fatal    | Signal a fatal error                       |

|           |                      | q_create   | Create a message queue                     |

|           |                      | q_delete   | Delete a message queue                     |

|           |                      | q_ident    | Identify a message queue                   |

|           |                      | q_receive  | Wait for a message at a queue              |

|           |                      | q_send     | Send a message to a queue                  |

|           |                      | q_urgent   | Put a message at the head of a queue       |

|           |                      | t_create   | Create a task                              |

|           |                      | t_ident    | Identify a task                            |

|           |                      | t_setpri   | Set a task priority                        |

|           |                      | t_start    | Start a task                               |

|           |                      | t_suspend  | Suspend a task                             |

|           |                      | tm_cancel  | Cancel a timer                             |

|           |                      | tm_evafter | Generate an event after a number of ticks  |

|           |                      | tm_evevery | Repeatedly generate periodic events        |

|           |                      | tm_tick    | Generate a tick                            |

|           |                      | tm_wkafter | Wait for a specified number of ticks       |

| pNA       | Network software     | bind       | Bind an address to a socket                |

|           |                      | socket     | Create a socket                            |

|           |                      | listen     | Listen for messages on a socket            |

|           |                      | close      | Close a socket                             |

| pREPC     | run-time C library   | various    | Re-entrant c-library functions             |

| pROBE     | Target component for |            | Component to which the host portion of the |

|           | debugger             |            | debugger (XRAY) connects.                  |

**Table 1 - Operating System Components**

# 3. Backplane Standard Analysis

Backplane summary:

- There are only two options for industrial control that make sense today VME and CompactPCI (referred to as cPCI)

- Other standards are either not rugged enough or are too costly for the application

- Both VME and cPCI have gone through a number of evolutionary steps with each step being backward compatible with the original specifications

- Both VME and cPCI have a broad industry following with new products being announced on a regular basis

- The growth in the VME market is expected to be less than the growth in the cPCI market

- In general, the cost of the backplanes and the boards for a cPCI solution are less than those of the VME solution

- In general, there are more cPCI board-level products available than VME board-level products

- The selection of VME board-level analog I/O products has decreased

- The high bandwidth, high availability systems needed in the telecommunications industry will result in a move to the AdvancedTCA platform. This will make AdvancedTCA the platform likely to see the most growth and evolution in the near future

- In general, industrial control applications do not need the features available in AdvancedTCA. Both VME and cPCI will continue to be the standards of choice for these applications.

VME vs cPCI selection:

- Both the VME and the cPCI standards are suitable for the application

- There is no need to move away from VME due to concerns over VME being close to the end of its lifecycle

- The cost, availability and features of the required circuit packs (CPU, AIO, DIO) will likely drive the selection of the standard

- Any suitable RTOS will function with either standard

Standards recommendation:

- Develop a cost model for both cPCI and VME

- Include all costs in the model including the cost to migrate the custom digital board to the cPCI form-factor

- Factors such as the long-term availability of the board-level products and board features should drive the backplane decision

# 4. VME bus Options

# 4.1. CPU Boards

CPU boards manufactured by the following vendors were considered:

- VMIC

- Force

- SBS Technologies

- Motorola

Only boards using the 6U form-factor were considered in the primary analysis. The decision not to consider 3U options was based on the following:

- 3U is seen rarely in VME systems

- There are only limited options for 3U CPU boards in the cPCI

- A 6U chassis allows a custom lower backplane to be used for analog and digital I/O

In looking at the many options available, the selection of candidate boards from each of the vendors was based on:

- Meeting the minimum specs DRAM, EPROM, flash boot EPROM or boot flash, at least 2 serial I/O ports preferably with front panel access, 100 BaseT Ethernet interface and industry standard PMC interface for add-on cards

- Availability of board support packages (BSPs) for major RTOS options (VxWorks, QNX, Linux)

- A board availability of at least 5 years from the date of introduction of the board

- Cost

- Minimum number of additional features that are not required for the control system

The selection of the CPU board was a two-step process. In the first step, a ranking matrix was created to provide an overall ranking of the candidate CPU boards. In the second step, more details were collected and analyzed for the top ranked boards.

# 4.1.1. Ranking Process

The ranking process included the criteria shown in the table below. The weights used for each criterion and the scoring system are included in the table. The ranking score for a board is the sum of the points received for each criterion multiplied by the weighting factor for that criterion. The maximum score possible for a board is 67.

| Criterion    | Weight | Rating         | _               |           |           | Rationale                                                   |  |          |  |                |  |                      |

|--------------|--------|----------------|-----------------|-----------|-----------|-------------------------------------------------------------|--|----------|--|----------------|--|----------------------|

| Age (y as of | 1.0    | <0.5:10        | <1:8            | 8         | <1.5:6    | Boards have a limited availability; older                   |  |          |  |                |  |                      |

| 01-Mar-04)   |        | <2:4           | >2: (           | )         |           | boards will become obsolete sooner                          |  |          |  |                |  |                      |

| Cost (k)     | 1.0    | < 2.5:10 < 3:8 |                 | 8 <3.5:6  |           | 8 <3.5:6                                                    |  | 8 <3.5:6 |  | < 3: 8 <3.5: 6 |  | Lower cost is better |

|              |        | <4:4           | <4.5            | : 2       | >4.5k: 0  |                                                             |  |          |  |                |  |                      |

| Maturity of  | 0.8    | >8m: 10        |                 | 5 to      | 8m: 8     | It takes at least 8 months after a board is                 |  |          |  |                |  |                      |

| BSP (months) |        | 3 to 5m: 6     | 5               | <3m       | n: 4      | released to get a mature BSP                                |  |          |  |                |  |                      |

| Backplane    | 0.7    | VME: 10        | VME: 10 cPCI: 8 |           | I: 8      | Need to respin the custom digital boards if we move to cPCI |  |          |  |                |  |                      |

| Features     | 0.7    | Start at 10    | ) poin          | ts and    | d reduce  |                                                             |  |          |  |                |  |                      |

|              |        | for inferio    | or/mis          | sing f    | features  |                                                             |  |          |  |                |  |                      |

| Processor    | 0.7    | PowerPC:       | : 10            | Pent      | ium-M: 8  | PowerPCs run cooler and are generally                       |  |          |  |                |  |                      |

|              |        | Pentium III:   |                 | um III: 6 |           | supported for longer. Pentium-M is on Intel's               |  |          |  |                |  |                      |

|              |        |                |                 |           |           | embedded roadmap and will be around longer                  |  |          |  |                |  |                      |

| Front panel  | 0.7    | 1 Etherne      | t & 2           | serial    | : 10      | The Ethernet i/f and the 2 serial i/f should be             |  |          |  |                |  |                      |

| access       |        | 2 of 3: 8      | 1 of            | 3: 6      | 0 of 3: 4 | accessible via the front panel                              |  |          |  |                |  |                      |

| RTOS (#      | 0.6    | >=3:10         |                 | 2:7.      | .5        | More RTOS support packages indicate the                     |  |          |  |                |  |                      |

| supported)   |        | 1:5            |                 | 0:0       |           | popularity of the board and maturity of the BSP             |  |          |  |                |  |                      |

| Bonus        | 0.5    | +3 for gig     | gΕ              |           |           | More is better                                              |  |          |  |                |  |                      |

| features     |        | +2 if featu    | ure dir         | rectly    | usable    |                                                             |  |          |  |                |  |                      |

|              |        | +1 if featu    | ure co          | uld b     | e used    |                                                             |  |          |  |                |  |                      |

### Table 2 - Ranking Criteria

The ranked list of processor boards is shown in the table below. The table includes both VME and cPCI boards. The details of the board features and board ranking are shown in section 7.

| Manufacturer    | Model                        | Bus  | Points |

|-----------------|------------------------------|------|--------|

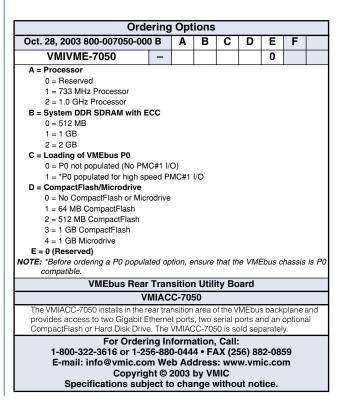

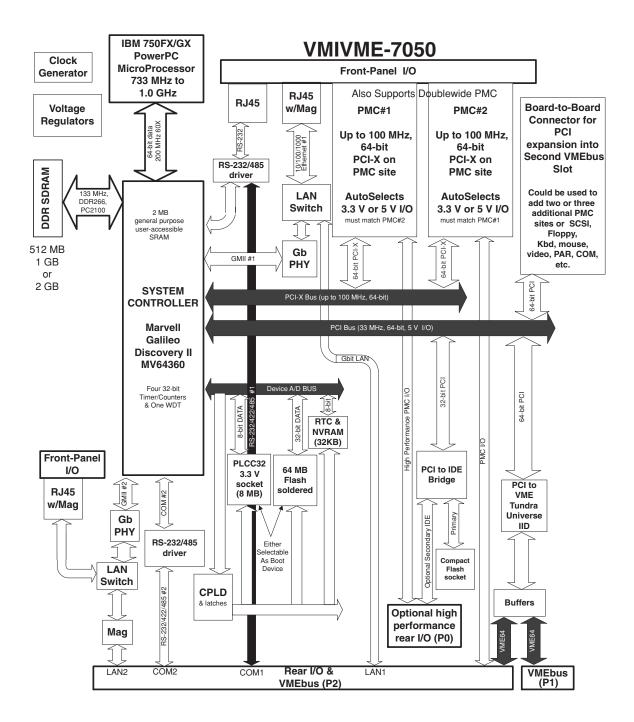

| GE Fanuc (VMIC) | VMIVME-7050-1001             | VME  | 57.6   |

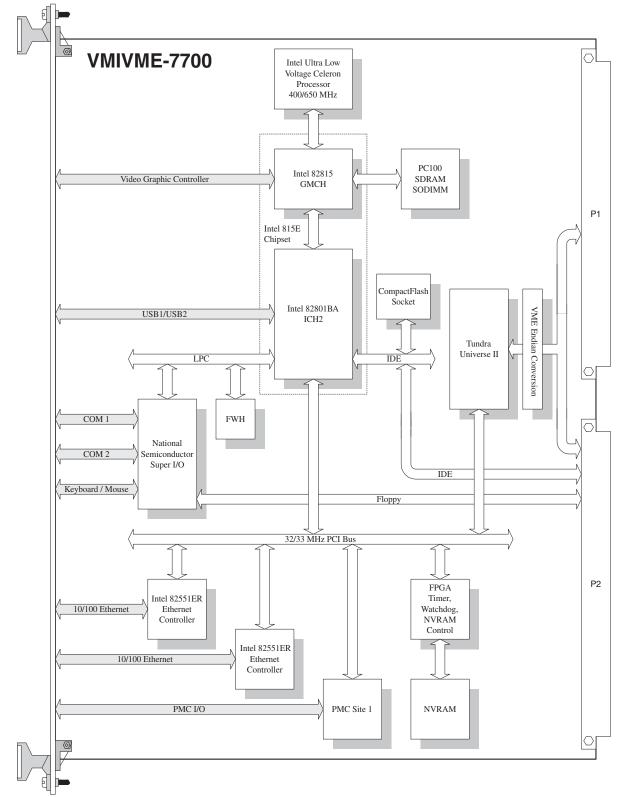

| GE Fanuc (VMIC) | VMIVME-7700-121 <sup>1</sup> | VME  | 57.1   |

| SBS             | VG5                          | VME  | 57.0   |

| Motorola        | MVME5500                     | VME  | 54.1   |

| GE Fanuc (VMIC) | VMICPCI-7806-111             | cPCI | 53.7   |

| SBS             | VG4                          | VME  | 53.0   |

| Force           | PowerCore CPCI-695           | cPCI | 51.1   |

| Force           | PowerCore CPU-695            | VME  | 51.0   |

| Motorola        | CPN5385                      | cPCI | 47.6   |

| SBS             | CT7                          | cPCI | 47.5   |

| SBS             | CR9                          | cPCI | 46.6   |

| SBS             | CT9                          | cPCI | 45.6   |

| Force           | CPCI-745                     | cPCI | 45.5   |

| SBS             | Power7E                      | VME  | 44.7   |

| Motorola        | MCP820                       | cPCI | 42.4   |

| Table 3 - | <b>CPU Ranked List</b> |

|-----------|------------------------|

|-----------|------------------------|

<sup>&</sup>lt;sup>1</sup> This board is a newly released board but was given high points for BSP maturity since data supplied by VMIC indicates that a number of BSPs with full support are already available.

# 4.1.2. Top Three

The ranking process separated the top 3 boards from the rest of the group. Each of these boards are suitable candidates for use in the control system. The following table provides additional details on each of the candidates.

| Model              | VMIVME-7050-<br>2000                              | VMIVME-7700-<br>121                                                         | VG5                                              | Comments                                                                                                                                        |

|--------------------|---------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Rank               | 1                                                 | 2                                                                           | 3                                                |                                                                                                                                                 |

| Age (yrs)          | 0.5                                               | 0                                                                           | 0.9                                              | all are less than a year                                                                                                                        |

| Cost (US\$)        | \$2,756                                           | \$2,601                                                                     | \$3,531                                          | <b>VG5:</b> approx 33% more than the others                                                                                                     |

| Processor          | PPC 750FX/GX                                      | Intel Celeron                                                               | PPC 7455                                         | 2 PowerPC options - run cooler                                                                                                                  |

| Speed<br>(GHz)     | 1.00                                              | 0.65                                                                        | 1.00                                             |                                                                                                                                                 |

| <u>`</u>           | 1 serial, 2 Ethernet                              | 2 serial, 2 Ethernet                                                        | 2 serial, 2 Ethernet                             | <b>7050:</b> either the terminal or the synch signal will need to use the rear P2 connector                                                     |

| Ethernet<br>Speed  | 2 gigE                                            | 2 10/100 MbitE                                                              | 1 gigE, 1 10/100<br>MbitE                        | <b>7700:</b> no gigE                                                                                                                            |

| Board              | VxWorks: released                                 | VxWorks: May-04                                                             | VxWorks: released                                |                                                                                                                                                 |

| Support            | Linux: late summer                                | Linux: released                                                             | Linux: not specified                             |                                                                                                                                                 |

| Packages           |                                                   | QNX: released                                                               | LynxOS: released                                 | 4                                                                                                                                               |

|                    |                                                   | Windows: released                                                           |                                                  |                                                                                                                                                 |

| PMC sites          | 2                                                 |                                                                             |                                                  | need 1 (for digital I/O)                                                                                                                        |

| Memory             | 512 MB SDRAM,<br>64.5 MB chip flash,<br>32K NVRAM | 512 MB SDRAM,<br>128 MB<br>compactFlash, 32K<br>NVRAM                       | 512 MB SDRAM,<br>128 MB chip flash,<br>24K NVRAM |                                                                                                                                                 |

| I/O                | 2 serial I/O; dual<br>gigE                        | 2 serial I/O; 2 USB;<br>2 10/100 BT                                         | 3 serial I/O; 1 gigE, 1<br>10/100 BT             |                                                                                                                                                 |

| Power Req<br>(max) | 3.8A @ 5V, 1.2 mA<br>@ +12V                       | 3.5A @ 5V, 1mA @<br>+/-12V                                                  | +5V, +3.3V                                       | <b>VG5:</b> VMEbus does not supply 3.3V => new chassis required                                                                                 |

| Bonus              | watchdog timer                                    | watchdog timer                                                              | watchdog timer                                   | Could be used to force a reboot if s/w locks up                                                                                                 |

| Features           | temp sense                                        |                                                                             | temp sense                                       | Could be used to detect overheating (fan failure)                                                                                               |

|                    | compactFlash                                      | compactFlash (part<br>of main memory)                                       |                                                  | <b>7050:</b> Allows flash to be added if necessary. <b>7700:</b> uses compactFlash for booting so flash memory could be increased on it as well |

|                    | built-in self test<br>(BIST)                      |                                                                             | planned                                          | Could integrate tests on RAM, COM ports and LAN into control s/w                                                                                |

|                    |                                                   | Enet boot                                                                   |                                                  | BIOS directly supports software boot from a server.<br>Would require additional effort on other boards                                          |

|                    |                                                   |                                                                             | conformal coating                                | Additional protection in a high-humidity environment                                                                                            |

|                    |                                                   |                                                                             | fanless cooling                                  | Board will continue to work even if the fan fails                                                                                               |

|                    | voltage sense                                     | byte-swapping h/w,<br>on-board video<br>controller, mouse &<br>keyboard I/f | optional dual CPU                                | Cool, but not useful                                                                                                                            |

### Table 4 - CPU Board Details

Based on the additional information for each board, the VMIVMI-7050 remains the top ranked board. The only potential difficulties seen in using this board are: one serial I/O channel can only be accessed through a rear connector (P2) and the degree of BSP support available. Depending on the RTOS selected and the timing of any purchases, the BSP availability will need to be investigated further.

# 4.2. Digital I/O

The digital input/output requirements for the control system are minimal. Rather than look at boardlevel products, the recommendation is that the less expensive, carrier-card technology be used. The Acromag PMC464 PMC module provides 64 TTL I/O lines with front panel or rear connector access. The card lists for \$600 US and is expected to be available for at least 10 years.

All 6U CPU boards considered – both VME and cPCI – have at least one site for a PMC module.

# 4.3. Analog I/O

Analog I/O board options are somewhat more limited for the VME bus than they were when the control system was first developed. The options are also more limited for the VME bus than they are for the cPCI bus. However, options remain for two analog I/O strategies. These strategies are: to use available board-level products offered by a few manufacturers or to use a carrier pack outfit with the appropriate industry pack modules for the application.

# 4.3.1. Carrier Packs

A number of manufacturers make carrier packs for the VME standard. The boards are simple and inexpensive so an exhaustive search for features is not necessary. The recommended carrier pack for the VME is the Acromag AVME9660. This is a 6U pack that holds up to 4 industry packs. The industry pack standard guarantees that modules from a number of vendors could be selected. All I/O signals on the pack are terminated on the front panel. The carrier pack is listed at \$590 US and is expected to be available for at least 7 years.

# 4.3.2. Analog Input